The silicon way to manufacture quantum computers at scale

High-performance, affordable quantum computers. Built for existing data centers.

Major partners powering our value chain

Quobly builds the industrial foundation for scalable quantum computing.

By combining silicon spin qubits with proven semiconductor manufacturing, we enable quantum systems that scale in performance, cost, and integration, ready for data centers and real-world applications.

1

million qubits on a single chip

90+

experts

65

patents filed

4

global locations

Quantum computing, from chip to datacenter

Industrial silicon qubits

Building quantum computers on proven semiconductor infrastructure: scalable silicon qubits on 300 mm wafers, engineered for fault-tolerant systems.

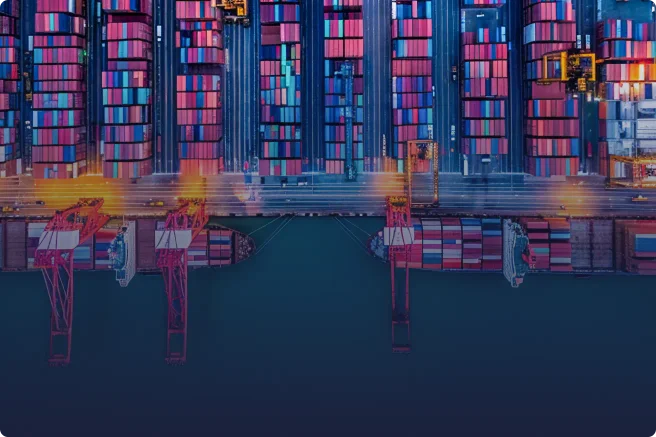

Datacenter-ready quantum systems

Rack-scale quantum computers designed for deployment in existing data centers, with modular upgrades across three generations turning quantum access into operational value.

The Quobly advantage

Fully integrated

1M qubits and control electronics in coin-sized chip and 3 datacenters racks

Built on silicon’s already amortized Capex

Thousands of identical chips, millions of qubits

Already at the industrial scale and requirements

Thousands of identical chips, millions of qubits

High-performance

Qubits at ~10 MHz, QEC-ready

Applications across industries

Quobly’s quantum computers are sufficiently fast, integrated and affordable to enable practical uses for industries that face challenges in chemistry, material science, optimization and logistic.